## Powerlink Microelectronics

### PL3536

### 高精度恒压/恒流、原边控制 PWM功率开关

### 芯片概述:

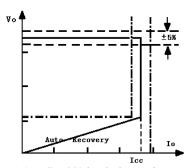

PL3536 是一款高效率、高集成度、原边调节的 PWM 功率 开关,其主要应用于小于 15W 的 AC/DC 反激式开关电源。PL3536 通过去除光耦以及次级控制电路,简化了充电器/适配器等传统的恒流/恒压的设计,从而实现高精度的电压和电流调节,调节波形如下图 1 所示。

PL3536 的复合模式的应用使得芯片能够实现低静态功耗、低音频噪音、高效率。内置的频率抖动可以很好的降低芯片的 EMI 以及 EMI 滤波成本,而且高集成的功率 MOSFET 能够降低外部 PCB 的面积以及系统的成本。

PL3536 同时具有多种保护功能:逐周期峰值电流检测、欠压保护、过压保护、VDD 钳位、过载保护等。

图 1 典型的恒流/恒压波形

### 管脚分布图:

### 主要特点:

- 内置高集成度的功率MOSFET

- +/-5%恒压调节

- 全电压范围内实现高精度电流调节

- 去除光耦和次级控制电路

- 内置高精度恒流调节的线电压补偿

- 内置变压器电感补偿

- 可编程的输出线补偿

- 内置可提高效率的自适应多模式 PWM/PFM控制

- 低启动电流

- 内置软启动

- 内置前沿消隐

- 逐周期电流限制

- 欠压保护

- 内置短路保护以及输出过压保护

#### 应用:

- 手机/无绳电话充电器

- 数码相机充电器

- 小功率电源适配器

- LED驱动

- 消费类的备用电源

### 1 概要

PL3536是款恒流/恒压原边控制的高性能离线反激式开关电源,其外部仅需少量元件。其内部集成了包括功率MOSFET以及原边控制模块等高压功率调节器。

PL3536适用于小于15W的AC/DC应用场合。其无需 光耦以及次级控制电路就能实现高精度的恒流/ 恒压功能。系统稳态时也无需额外的补偿电路, 从而能够得到精准的电压/电流控制。

与传统的次级调节方式相比,PL3536能够降低系统元器件数量,PCB面积以及整个系统成本,且可以提高系统的效率及稳定性。

PL3536复合模式的应用使得芯片能够实现低静态功耗、低音频噪音、高效率。在恒流模式以及系统重载下,芯片会工作在PFM模式,系统正常时,PL3536工作在PWM模式。这种绿色模式会大大提高系统的效率,同时能够节省能耗。

PL3536 具有多种保护功能以应对系统的各种异常状态。主要包括:限流保护、欠压保护、过压保护、VDD 钳位等。系统发生异常时,芯片将被保护,直到系统恢复正常状态。

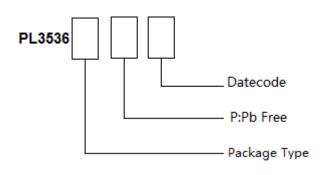

PL3536提供DIP8封装。

### 2 特性

- 内置高集成度的功率MOSFET

- +/-5%恒压调节

- 全电压范围内精准的恒流调节

- 去除光耦和次级恒流恒压控制电路

- 内置高精度恒流调节的线电压补偿

- 内置变压器电感补偿

- 可编程的输出线补偿

- 内置可提高效率的自适应多模式PWM/PFM控制

- 低启动电流

- 内置软启动

- 内置短路保护

- 内置前沿消隐

- 过流保护

- 过压保护

- VDD钳位保护

- 欠压保护

- 过载保护

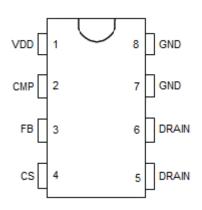

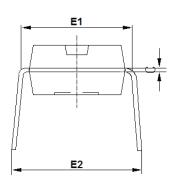

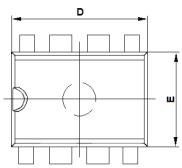

# 3 管脚分布图

DIP-8的管脚图如下图所示:

# 4 管脚描述

| 管脚名   | 描述                                   |

|-------|--------------------------------------|

| VDD   | 芯片电源输入                               |

| CMP   | 误差放大器输出,用于环路补偿                       |

| FB    | 通过电阻分压连接到辅助绕组,该管脚用于检测输出信号并调节芯片的恒流/恒压 |

| CS    | 通过检测连接CS到地电阻的电压来反映原边电感电流             |

| DRAIN | 高压MOSFET的漏端,连接到变压器                   |

| GND   | 芯片地                                  |

# 5 最大额定值

| 参数                      | 符号    | 范围            | 单位         |

|-------------------------|-------|---------------|------------|

| VDD 电压(1 脚)             | VDD   | -0.3到VDDc1amp | V          |

| CMP 输入(2 脚)             | CMP   | -0.3 到 7      | V          |

| CS 输入(4 脚)              | CS    | -0.3到7        | V          |

| FB 输入(3 脚)              | FB    | -0.3到7        | V          |

| 最大工作结温                  | Tjmax | 150           | $^{\circ}$ |

| 存储温度                    | Tsto  | -55 到 150     | $^{\circ}$ |

| 焊接温度(Soldering, 10secs) | Tlea  | 260           | $^{\circ}$ |

**注释:**超过最大额定值可能损毁器件;超过推荐工作范围的芯片功能特性不能保证;长时间工作于最大额定条件下可能会影响器件的稳定性。

# 6 推荐工作条件

| 参数     | 最小  | 最大   | 单位         |

|--------|-----|------|------------|

| 工作环境温度 | -40 | +105 | $^{\circ}$ |

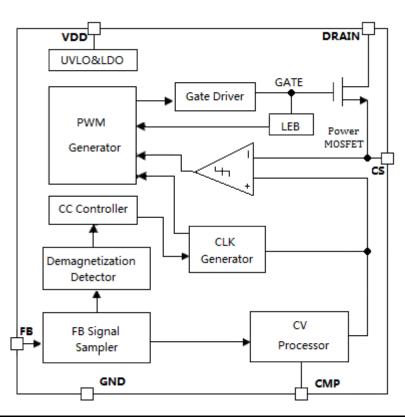

# 7 结构框图

# 8 电气特性

(无特殊说明, 其测试条件为: VDD =16V, TA = 25℃)

| 参数              | 符号        | 测试条件                     | 最小    | 典型    | 最大    | 单位   |  |

|-----------------|-----------|--------------------------|-------|-------|-------|------|--|

| 电源电压 (VDD)      |           |                          |       |       |       |      |  |

| 启动电流            | I DD_sd   | VDD=16V                  |       | 1. 1  | 20    | uA   |  |

| 工作电流            | I DD_op   | FB=2V, CS=0V,<br>VDD=20V |       | 1     | 1. 5  | mA   |  |

| VDD 进入欠压阈值      | UVLO(ON)  | VDD 下降                   | 8. 1  | 9.0   | 9.8   | V    |  |

| VDD 退出欠压阈值      | UVLO(0FF) | VDD 上升                   | 13. 5 | 14. 5 | 15. 5 | V    |  |

| VDD 过压阈值        | OVP       | VDD 上升直到栅极<br>关断         | 26    | 27. 5 | 29    | V    |  |

| VDD 齐纳击穿电压      | VDD_zb    | IDD=10mA                 | 30    | 32. 5 | 35    | V    |  |

| 频率 (FOSC)       | 频率(FOSC)  |                          |       |       |       |      |  |

| IC 最大频率         | Freq_Max  |                          | 55    | 60    | 65    | KHz  |  |

| 频率抖动范围          | △f/Freq   |                          |       | +/-5  |       | %    |  |

| 电流检测 (SENSE)    |           |                          |       |       |       |      |  |

| 导通 LEB 时间       | TLEB      |                          |       | 500   |       | ns   |  |

| 过流阈值            | Vocp      |                          | 980   | 1000  | 1020  | mV   |  |

| 输入阻抗            | ZSENSE    |                          | 100   |       |       | Kohm |  |

| 软启动             | T_sst     |                          |       | 10    |       | ms   |  |

| 恒流/恒压控制 (CC/CV) |           |                          |       |       |       |      |  |

| EA 的基准电压        | Vref_EA   |                          | 1. 98 | 2     | 2.02  | V    |  |

| EA 的直流增益        | Gain      |                          |       | 70    |       | dB   |  |

| 最大输出线补偿电流       | I_CMP_MAX | FB=2V, CMP=0V            |       | 38    |       | uA   |  |

| 采样端 LEB 时间      | SLEB      |                          |       | 2     |       | us   |  |

| 功率 MOSFET       |           |                          |       |       |       |      |  |

| MOSFET 漏源击穿电压   | BVdss     |                          | 600   |       |       | V    |  |

| 导通电阻            | Rdson     | Static, Id=0.5A          |       |       | 4.6   | Ω    |  |

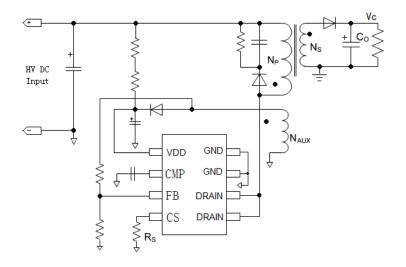

### 9 典型应用

### 应用说明:

PL3536 为小功率的适配器/充电器应用提供了很有效的解决方案,其新颖的恒流/恒压控制使得系统不需要次级反馈电路,并能实现高精度的恒流/恒压输出,从而满足更严格的能源损耗要求。

### 9.1 启动电流和工作电流

PL3536 具有低的启动电流,因而可以采用大的启动电阻以及小的 VDD 电容以降低应用中的功率损耗。

PL3536 的工作电流小至 1mA, 再加上特有的复合模式控制, 从而提高了系统的效率, 特别是系统处于轻载条件下。

#### 9.2 软启动

系统上电后,当 VDD 达到 UVLO(0FF),芯片开始工作,其振荡频率及 CS 端的峰值电压会逐步增加,因而会降低外部元件在芯片启动过程中的电压应力。芯片每次重启都伴随着软启动。

#### 9.3 恒压/恒流调节

恒压/恒流的调节主要是基于系统工作在 DCM 模式。

工作于 DCM 模式的反激式开关电源,可以通过辅助绕组来采样输出电压。功率管导通时,原边电流逐步增加,功率管关闭后,原边电流传输到次

级,并形成次级电流 $I_{Spk}$ 。

$$I_{Spk} = \frac{N_P}{N_S} \bullet I_{Ppk} \tag{1}$$

IPpk 为功率管关闭后的原边峰值电流。

通过次级绕组和辅助绕组之间的耦合,输出电压可以下式得到:

$$V_o = \frac{Ns \cdot V_{aux}}{N_{aux}} - \Delta V \tag{2}$$

$V_{aux}$ 是辅助绕组的电压, $\Delta V$ 是次级二极管的压降。

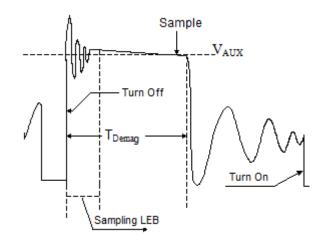

图 2 辅助绕组电压波形

基于内部的时序控制,辅助绕组的电压可以通过 对连接于辅助绕组和 FB 之间的分压电阻采样得 到。在恒压工作模式中,内部误差放大器对采样

的电压进行调节,从而得到恒定的输出电压。 在恒流工作模式中,不管系统的输出电压大小, 芯片会保持输出电流恒定。

#### 9.4 可编程恒流点及输出功率

在小于 15W 的应用中, CS 端不同的采样电阻会得到不同的恒流点。输出功率的大小可通过调节 CS 端的采样电阻实现, 采样电阻越大, 恒流点越小, 同时输出功率也越小。

### 9.5 开关频率及电感补偿

PL3536 的开关频率大小取决于系统负载状态以及芯片工作模式。恒压模式中芯片通常工作在最大频率。假设系统的效率是 100%, 那么输出功率可由下式给出:

$$Po = \frac{1}{2} L_{m} f_{sw} I_{Ppk}^{2} = Vo \bullet Io$$

(3)

Lm 是原边绕组的电感值, *IPpi* 是原边绕组的峰值电流。

从上式中可看出,Lm 的变化会导致功率的变化,同时也影响恒流模式中的输出电流的恒定性,在

大规模应用中会使得芯片的一致性变差。为了降低原边绕组电感量变化产生的效应,芯片内置了补偿电路,使得电感值和频率的乘积恒定,并矫正电感量的误差,从而得到准确的恒流点。

### 9.6 可编程的输出线补偿

由原边反馈原理可知,输出电压通过辅助绕组采 样得到,这样会影响恒压的精度,为提高负载调 节率,芯片内置了输出线补偿电路,那么系统在 空载和满载状态时,输出电压可保持恒定。

不同的应用中,通过调节连接于 FB 端的分压电阻可得到不同的线补偿量, FB 端的分压电阻越大,那么补偿量也越大。

### 9.7 保护功能

PL3536 内置了多种保护功能,包括:逐周期限流保护,VDD 钳位保护,软启动,欠压保护,短路保护,开路保护,过压保护,过载保护等。

当 PL3536 的 VDD 电压下降到 UVLO(ON),或者 VDD 电压上升到 OVP 阈值,芯片将不工作,同时会进入重启状态。

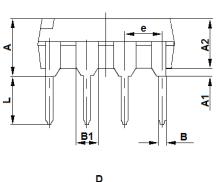

## 10 封装

### DIP8 封装

DIP8 封装尺寸:

| 符号 | 毫米尺寸       |        | 英寸尺寸      |       |

|----|------------|--------|-----------|-------|

|    | 最小         | 最大     | 最小        | 最大    |

| А  | 3.710      | 5.334  | 0.146     | 0.210 |

| A1 | 0.381      |        | 0.015     |       |

| A2 | 2.921      | 4.953  | 0.115     | 0.195 |

| В  | 0.350      | 0.650  | 0.014     | 0.026 |

| B1 | 1.524(BSC) |        | 0.06(BSC) |       |

| С  | 0.200      | 0.360  | 0.008     | 0.014 |

| D  | 9.000      | 10.160 | 0.354     | 0.400 |

| E  | 6.096      | 7.112  | 0.240     | 0.280 |

| E1 | 7.320      | 8.255  | 0.288     | 0.325 |

| е  | 2.540(BSC) |        | 0.1(BS    | SC)   |

| L  | 2.921      | 3.810  | 0.115     | 0.150 |

| E2 | 7.620      | 10.920 | 0.300     | 0.430 |

# 11 注意事项

聚元有权在任何时刻修改其产品信息, 恕不另行通知; 客户在下订单前应确保产品信息的及时更新和完整性。