#### **General Description**

The LSP5526 is a monolithic synchronous buck regulator. The device integrates  $95m\Omega$  MOSFETS that provide 2A continuous load current over a wide operating input voltage of 4.5V to 23V. Current mode control provides fast transient response and cycle-by-cycle current limit. An adjustable soft-start prevents inrush current at turn on.

#### **Features**

- 2A Output Current

- Wide 4.5V to 23V Operating Input Range

- Integrated Power MOSFET Switches

- Output Adjustable from 0.925V to 18Vin

- Up to 96% Efficiency

- Programmable Soft-Start

- Stable with Low ESR Ceramic Output Capacitors

- Fixed 340KHZ Frequency

- Cycle by Cycle Over Current Protection

- Input Under Voltage Lockout

- Package: SOP-8L

### **Applications**

- Distributed Power Systems

- Networking Systems

- FPGA, DSP, ASIC Power Supplies

- Green Electronics/ Appliances

- Notebook Computers

Please be aware that an **Important Notice** concerning availability, disclaimers, and use in critical applications of LSC products is at the end of this document.

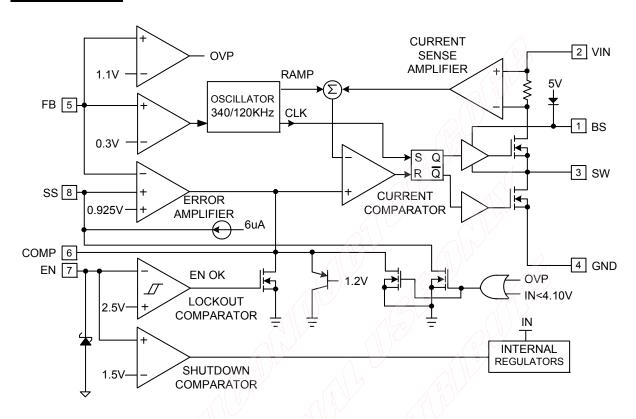

### **Block Diagram**

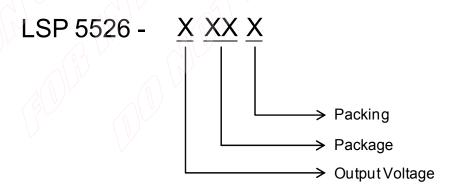

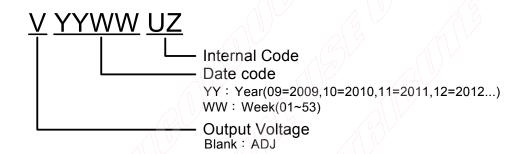

## **Ordering Information**

| Output Voltage | Package     | Packing        |

|----------------|-------------|----------------|

| Blank : ADJ    | S8 : SOP-8L | A: Tape & Reel |

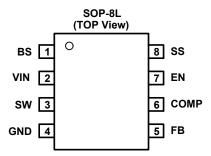

## **Pin Assignment**

## **Pin Descriptions**

| Pin Name | Name | Pin Description                                                                                                                                                                                                                                                                 |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | BS   | Bootstrap. This pin acts as the positive rail for the high-side switch's gate driver. Connect a 0.01uF capacitor between BS and SW.                                                                                                                                             |

| 2        | VIN  | Input Supply. Bypass this pin to GND with a low ESR capacitor. See Input Capacitor in the Application Information section.                                                                                                                                                      |

| 3        | SW   | Switch Output. Connect this pin to the switching end of the inductor.                                                                                                                                                                                                           |

| 4        | GND  | Ground.                                                                                                                                                                                                                                                                         |

| 5        | FB   | Feedback Input. The voltage at this pin is regulated to 0.925V. Connect to the resistor divider between output and ground to set output voltage.                                                                                                                                |

| 6        | СОМР | Compensation Pin. See Stability Compensation in the Application Information section.                                                                                                                                                                                            |

| 7        | EN   | Enable Input. When higher than 2.7V, this pin turns the IC on. When lower than 1.1V, this pin turns the IC off. Output voltage is discharged when the IC is off. This pin should not be left open. Recommend to put a $100 \text{K}\Omega$ pull-up resistor to Vin for startup. |

| 8        | SS   | Soft-Start Control Input. SS controls the soft-start period. Connect a capacitor from SS to GND to set the soft-start period. A 0.1uF capacitor sets the soft-start period to 15ms. To disable the soft-start feature, leave SS unconnected.                                    |

### **Absolute Maximum Ratings**(at T<sub>A</sub>=25°C)

Note: Operate over the "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to such conditions for extended time may still affect the reliability of the device.

| Characteristics                                 | Value                                                     | Unit      |

|-------------------------------------------------|-----------------------------------------------------------|-----------|

| Input Supply Voltage                            | -0.3 to 25                                                | V         |

| SW Voltage                                      | -0.3 to V <sub>IN</sub> + 0.3                             | V         |

| BS Voltage                                      | V <sub>SW</sub> – 0.3 to V <sub>SW</sub> + 6              | V         |

| EN, FB, COMP Voltage                            | -0.3 to 5                                                 | V         |

| Continuous SW Current                           | Internally limited                                        | А         |

| Maximum Junction Temperature                    | 150                                                       | °C        |

| Storage Temperature Range                       | -65 to 150                                                | °C        |

| SOP-8L Thermal Resistance (Junction to Case)    | 60                                                        | °C/W      |

| SOP-8L Thermal Resistance (Junction to Ambient) | 150                                                       | °C/W      |

| SOP-8L Power dissipation                        | 810                                                       | mW        |

| Moisture Sensitivity (MSL)                      | Please refer the MSL label on the I bag/carton for detail | C package |

Note1: Ratings apply to ambient temperature at 25°C

### **Recommended Operating Conditions**

| Characteristics                | Min | Max  | Unit |

|--------------------------------|-----|------|------|

| Input Supply Voltage           | 4.5 | 23   | V    |

| Operating Junction Temperature | -20 | +125 | °C   |

## **Electrical Characteristics**

(T<sub>A</sub>=25°C, unless otherwise specified)

| Characteristics                             | Symbol            | Conditions                                   | Min                   | Тур   | Max   | Unit |

|---------------------------------------------|-------------------|----------------------------------------------|-----------------------|-------|-------|------|

| Feedback Voltage                            | $\mathbf{V}_{FB}$ | 4.5V ≤ VIN ≤ 23V                             | 0.900                 | 0.925 | 0.950 | V    |

| Feedback Overvoltage Threshold              |                   |                                              | $\bigcap(\mathbb{N})$ | 1.1   |       | V    |

| High-Side Switch-On Resistance*             |                   |                                              |                       | 95    |       | mΩ   |

| Low-Side Switch-On Resistance*              |                   |                                              | V                     | 95    |       | mΩ   |

| High-Side Switch Leakage                    |                   | V <sub>EN</sub> = 0V, V <sub>SW</sub> = 0V   |                       |       | 10    | uA   |

| Upper Switch Current Limit                  |                   | Minimum Duty Cycle                           | 2.7                   | 3.5   |       | Α    |

| COMP to Current<br>Limit Transconductance   | G <sub>COMP</sub> |                                              |                       | 3.3   |       | A/V  |

| Error Amplifier Transconductance            | G <sub>EA</sub>   | $\Delta I_{COMP} = \pm 10 \text{uA}$         |                       | 920   |       | uA/V |

| Error Amplifier DC Gain*                    | <b>A</b> VEA      |                                              |                       | 480   | 9     | V/V  |

| Switching Frequency                         | f <sub>SW</sub>   |                                              |                       | 340   |       | KHz  |

| Short Circuit Switching Frequency           | (                 | V <sub>FB</sub> = 0                          |                       | 120   |       | KHz  |

| Maximum Duty Cycle                          | D <sub>MAX</sub>  | V <sub>FB</sub> = 0.8V                       | /\ 0,                 | 92    |       | %    |

| Minimum On Time*                            |                   |                                              | $\Omega V$            | 220   |       | nS   |

| EN Shutdown Threshold Voltage               |                   | V <sub>EN</sub> Rising                       | 1.1                   | 1.4   | 2     | V    |

| EN Shutdown Threshold Voltage<br>Hysteresis |                   |                                              |                       | 180   |       | mV   |

| EN Lockout Threshold Voltage                |                   |                                              | 2.2                   | 2.5   | 2.7   | V    |

| EN Lockout Hysteresis                       | 1                 |                                              |                       | 130   |       | mV   |

| Supply Current in Shutdown                  |                   | V <sub>EN</sub> = 0                          |                       | 0.3   | 3.0   | uA   |

| IC Supply Current in Operation              |                   | V <sub>EN</sub> = 3V, V <sub>FB</sub> = 1.0V |                       | 1.3   | 1.5   | mA   |

| Input UVLO Threshold Rising                 | UVLO              | V <sub>EN</sub> Rising                       | 3.80                  | 4.05  | 4.40  | V    |

| Input UVLO Threshold Hysteresis             | (                 |                                              |                       | 100   |       | mV   |

| Soft-start Current                          | (1)               | V <sub>SS</sub> = 0V                         |                       | 6     |       | uA   |

| Soft-start Period                           |                   | C <sub>SS</sub> = 0.1uF                      |                       | 15    |       | mS   |

| Thermal Shutdown Temperature*               |                   | Hysteresis =25°C                             |                       | 160   |       | °C   |

Note: \* Guaranteed by design.

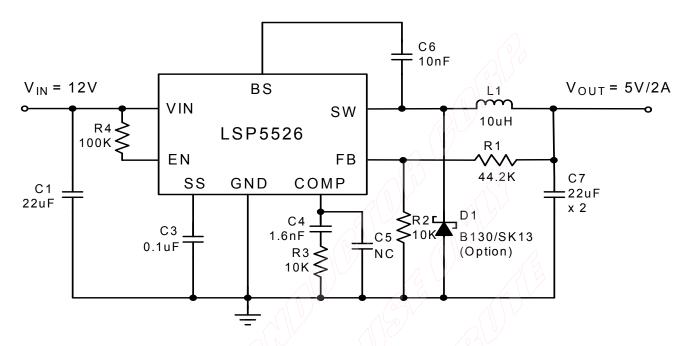

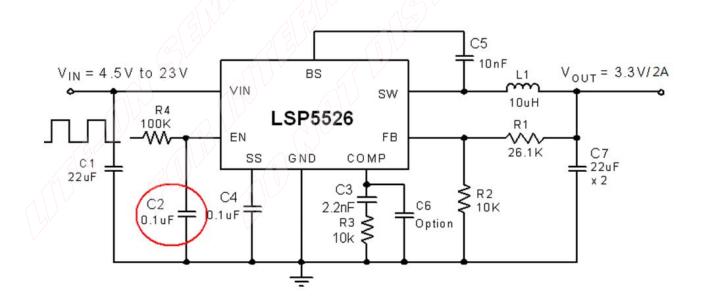

### **Application Circuit**

LSP5526 Circuit, 5V/2A output

LSP5526 Circuit, 3.3V/2A output

Note: C2 is required for separate EN signal.

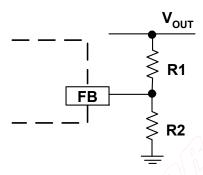

#### **Output Voltage Setting**

Figure 1. Output Voltage Setting

Figure 1 shows the connections for setting the output voltage. Select the proper ratio of the two feedback resistors R1 and R2 based on the output voltage. Typically, use R2  $\approx$  10K $\Omega$  and determine R1 from the following equation:

| VOUE |         |       |

|------|---------|-------|

| VOUT | R1      | R2    |

| 1.0V | 1.0 ΚΩ  | 12 KΩ |

| 1.2V | 3.0 ΚΩ  | 10 KΩ |

| 1.8V | 9.53 ΚΩ | 10 KΩ |

| 2.5V | 16.9 ΚΩ | 10 KΩ |

| 3.3V | 26.1 ΚΩ | 10 ΚΩ |

| 5V   | 44.2 KΩ | 10 ΚΩ |

| 12V  | 121 ΚΩ  | 10 ΚΩ |

Table1 - Recommended Resistance Values

$$R1 = R2 \left( \frac{V_{OUT}}{0.925 \text{V}} - 1 \right) \tag{1}$$

#### **Inductor Selection**

The inductor maintains a continuous current to the output load. This inductor current has a ripple that is dependent on the inductance value: higher inductance reduces the peak-to-peak ripple current. The trade off for high inductance value is the increase in inductor core size and series resistance, and the reduction in current handling capability. In general, select an inductance value L based on the ripple current requirement:

$$L = \frac{V_{OUT} \bullet (V_{IN} - V_{OUT})}{V_{IN} f_{SW} I_{OUTMAX} K_{RIPPLE}}$$

(2)

w here VIN is the input voltage, VOUT is the output voltage, fSW is the switching frequency, IOUTMAX is the maximum output current, and KRIPPLE is the ripple factor. Typically, choose KRIPPLE = 30% to correspond to the peak-to-peak ripple current being 30% of the maximum output current.

With this inductor value, the peak inductor current is IOUT • (1 + KRIPPLE / 2). Make sure that this peak inductor current is less than the upper switch current limit. Finally, select the inductor core size so that it does not saturate at the current limit. Typical inductor values for various output voltages are shown in Table 2.

| Ī | V <sub>OUT</sub> | 1.0V  | 1.2V  | 1.5V | 1.8V | 2.5V | 3.3V | 5V   | 9V   |

|---|------------------|-------|-------|------|------|------|------|------|------|

| Ī | L                | 4.7uH | 4.7uH | 10uH | 10uH | 10uH | 10uH | 10uH | 33uH |

**Table 2. Typical Inductor Values**

#### **Input Capacitor**

The input capacitor needs to be carefully selected to maintain sufficiently low ripple at the supply input of the converter. A low ESR capacitor is highly recommended. Since large current flows in and out of this capacitor during switching, its ESR also affects efficiency.

The input capacitance needs to be higher than 10uF. The best choice is the ceramic type; however, low ESR tantalum or electrolytic types may also be used provided that the RMS ripple current rating is higher than 50% of the output current. The input capacitor should be placed close to the VIN and GND pins of the IC, with the shortest traces possible. In the case of tantalum or electrolytic types, they can be further away if a small parallel 0.1uF ceramic capacitor is placed right next to the IC.

#### **Output Capacitor**

The output capacitor also needs to have low ESR to keep low output voltage ripple. In the case of ceramic output capacitors, RESR is very small and does not contribute to the ripple. Therefore, a lower capacitance value can be used for ceramic capacitors. In the case of tantalum or electrolytic capacitors, the ripple is dominated by RESR multiplied by the ripple current. In that case, the output capacitor is chosen to have sufficiently low ESR.

For ceramic output capacitors, typically choose a capacitance of about 22uF. For tantalum or electrolytic capacitors, choose a capacitor with less than  $50m\Omega$  ESR.

#### **Optional Schottky Diode**

During the transition between high-side switch and low-side switch, the body diode of the low side power MOSFET conducts the inductor current. The forward voltage of this body diode is high. An optional Schottky diode may be paralleled between the SW pin and GND pin to improve overall efficiency. Table 3 lists example Schottky diodes and their Manufacturers.

Table 3-Diode Selection Guide

| Part Number | Voltage/Current<br>Rating | Vendor                      |

|-------------|---------------------------|-----------------------------|

| B130        | 30V, 1A                   | Lite-on semiconductor corp. |

| SK13        | 30V, 1A                   | Lite-on semiconductor corp. |

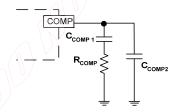

#### **Stability Compensation**

C<sub>COMP2</sub> is needed only for high ESR output capacitor Figure 2. Stability Compensation

The feedback loop of the IC is stabilized by the components at the COMP pin, as shown in Figure 2. The DC loop gain of the system is determined by the following equation:

$$A_{VDC} = \frac{0.925 \, V}{I_{OUT}} A_{VEA} \, G_{COMP}$$

(4)

The dominant pole P1 is due to  $C_{COMP1}$ :

$$f_{P1} = \frac{G_{EA}}{2\pi A_{VEA} C_{COMP1}} \tag{5}$$

The second pole P2 is the output pole:

$$f_{P2} = \frac{I_{OUT}}{2\pi V_{OUT} C_{OUT}}$$

(6)

The first zero Z1 is due to  $R_{COMP}$  and  $C_{COMP1}$ :

$$f_{Z1} = \frac{1}{2\pi R_{COMP} C_{COMP1}}$$

(7)

And finally, the third pole is due to  $R_{COMP}$  and  $C_{COMP2}$  (if  $C_{COMP2}$  is used):

$$f_{P3} = \frac{1}{2\pi R_{COMP} C_{COMP2}} \tag{8}$$

The following steps should be used to compensate the IC:

STEP1. Set the crossover frequency at 1/10 of the switching frequency via  $R_{COMP}$ :

$$R_{COMP} = \frac{2\pi V_{OUT} C_{OUT} f_{SW}}{10G_{EA} G_{COMP} \bullet 0.925V} \quad (9)$$

But limit  $R_{COMP}$  to  $10K\Omega$  maximum.

STEP2. Set the zero fZ1 at 1/4 of the crossover frequency. If  $R_{COMP}$  is less than 10K $\Omega$ , the equation for  $C_{COMP}$  is:

$$C_{COMP1} = \frac{0.637}{R_{COMP} \times fc}$$

(F) (10)

STEP3. If the output capacitor's ESR is high enough to cause a zero at lower than 4 times the crossover frequency, an additional compensation capacitor  $C_{COMP2}$  is required. The condition for using  $C_{COMP2}$  is:

$$\pi \times Cout \times Resr \times fs \ge 1 \tag{11}$$

And the proper value for  $C_{\text{COMP2}}$  is:

$$C_{COMP2} = \frac{C_{OUT}R_{ESRCOUT}}{R_{COMP}}$$

(12)

A reference table as follows:

| Vin Range<br>(V) | Vout<br>(V) | Cout                  | Rcomp (R3)<br>(kΩ) | Ccomp (C4)<br>(nF) | Ccomp2 (C5)<br>(pF) | Inductor<br>(uH) |

|------------------|-------------|-----------------------|--------------------|--------------------|---------------------|------------------|

| 5 – 12           | 1.0         |                       | 3.3                | 5.6                | none                | 4.7              |

| 5 - 15           | 1.2         |                       | 3.9                | 4.7                | none                | 4.7              |

| 5 - 23           | 1.8         | 22uF x2               | 5.6                | 3.3                | none                | 10               |

| 5 - 23           | 2.5         | Ceramic               | 8.2                | 2.2                | none                | 10               |

| 5 - 23           | 3.3         |                       | 10                 | 2 (\)              | none                | 10               |

| 5 - 23           | 5           |                       | 10                 | 3.3                | none                | 10               |

| 5 - 12           | 1.0         |                       |                    |                    |                     | 4.7              |

| 5 - 15           | 1.2         | 470E/                 |                    |                    |                     | 4./              |

| 5 - 23           | 1.8         | 470uF/<br>6.3V/       | 10                 | 6.8                | 680                 |                  |

| 5 - 23           | 2.5         | $120\mathrm{m}\Omega$ | 10                 | 0.6                | 000                 | 10               |

| 5 - 23           | 3.3         | 12011122              |                    | (\)                | 2                   | 10               |

| 5 - 23           | 5           |                       |                    |                    |                     |                  |

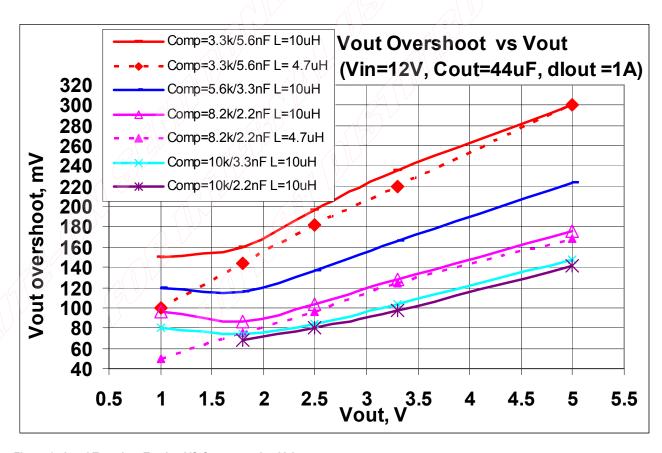

Figure 3. Load Transient Testing VS Compensation Value

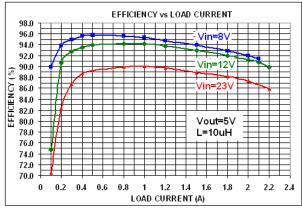

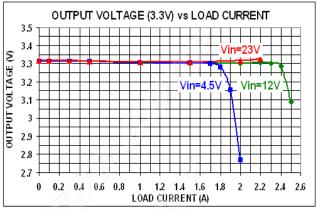

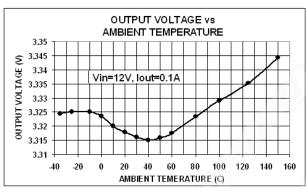

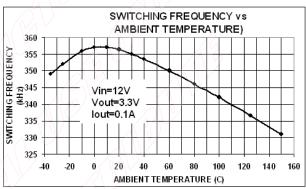

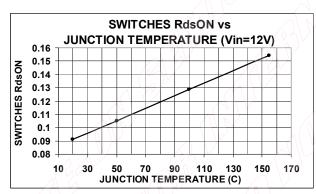

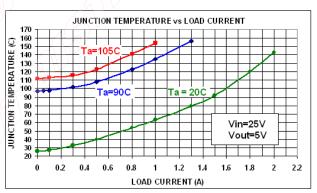

## **Typical Characteristics**

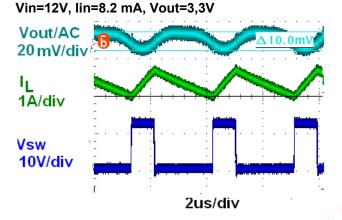

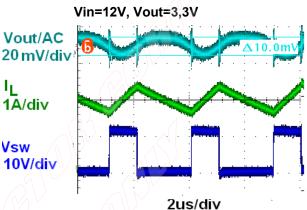

**Light Load Operation (No load)**

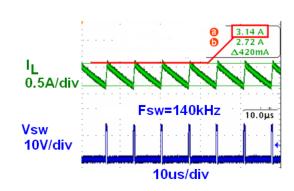

**Heavy Load Operation (2A Load)**

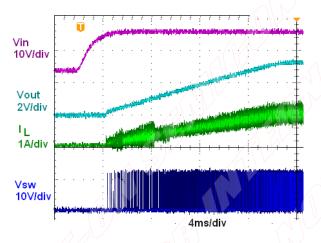

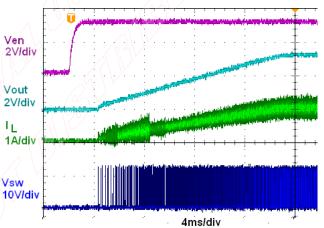

Startup Vin=12V, Vout=3.3V, Iout=1A through Vin.

through Enable.

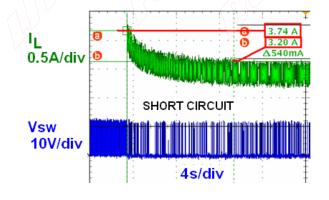

### **Short Circuit Protection Vin=12V**

## **Typical Characteristics (Continued)**

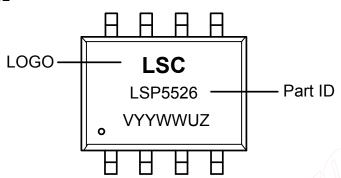

## **Marking Information**

SOP-8L

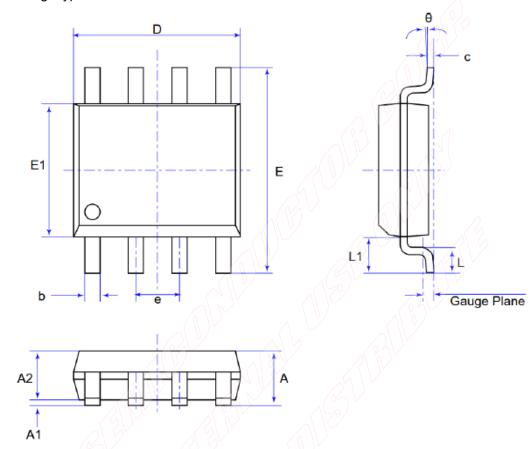

## **Mechanical Information**

(1) Package type: SOP-8L

Unit: mm

|                                        |          | Offic : Ithiri |  |  |

|----------------------------------------|----------|----------------|--|--|

| Symbol                                 | Min      | Max            |  |  |

|                                        |          | 1.75           |  |  |

| A1                                     | 0.10     | 0.25           |  |  |

| A2                                     | 1.25     | 1.65           |  |  |

| \ \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | 0.33     | 0.51           |  |  |

| \c \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | 0.10     | 0.26           |  |  |

| D                                      | 4.70     | 5.10           |  |  |

| E                                      | 5.80     | 6.20           |  |  |

| E1                                     | 3.70     | 4.10           |  |  |

| е                                      | 1.27     | REF            |  |  |

| L                                      | 0.40     | 1.27           |  |  |

| L1                                     | 1.04 REF |                |  |  |

| Gauge Plane                            | 0.25     | BSC            |  |  |

| θ                                      | 0°       | 8°             |  |  |

### MSL (Moisture Sensitive Level) Information

#### IPC/JEDEC J-STD-020D.1 Moisture Sensitivity Levels Table

|       |                        |                   |                           | S                | OAK REQUIR      | EMENTS                   |               |  |  |

|-------|------------------------|-------------------|---------------------------|------------------|-----------------|--------------------------|---------------|--|--|

|       | FLOOR LIFE             |                   |                           |                  |                 | Accelerated Equivalent 1 |               |  |  |

| LEVEL |                        |                   | Standard                  |                  | eV<br>0.40-0.48 | eV<br>0.30-0.39          | CONDITION     |  |  |

|       | TIME                   | CONDITION         | TIME<br>(hours)           | CONDITION        |                 | TIME<br>(hours)          | CONDITION     |  |  |

| 1     | Unlimited              | ≤30 °C /85%<br>RH | 168<br>+5/-0              | 85 °C /85%<br>RH | NA              | NA                       | NA            |  |  |

| 2     | 1 year                 | ≤30 °C /60%<br>RH | 168<br>+5/-0              | 85 °C /60%<br>RH | NA              | NA                       | NA            |  |  |

| 2a    | 4 weeks                | ≤30 °C /60%<br>RH | 696 <sup>2</sup><br>+5/-0 | 30 °C /60%<br>RH | 120<br>-1/+0    | 168<br>-1/+0             | 60 °C/ 60% RH |  |  |

| 3     | 168 hours              | ≤30 °C /60%<br>RH | 192 <sup>2</sup><br>+5/-0 | 30 °C /60%<br>RH | 40<br>-1/+0     | 52<br>-1/+0              | 60 °C/ 60% RH |  |  |

| 4     | 72 hours               | ≤30 °C /60%<br>RH | 96 <sup>2</sup><br>+2/-0  | 30 °C /60%<br>RH | 20<br>+0.5/-0   | 24<br>+0.5/-0            | 60 °C/ 60% RH |  |  |

| 5     | 48 hours               | ≤30 °C /60%<br>RH | 72 <sup>2</sup><br>+2/-0  | 30 °C /60%<br>RH | 15<br>+0.5/-0   | 20<br>+0.5/-0            | 60 °C/ 60% RH |  |  |

| а     | 24 hours               | ≤30 °C /60%<br>RH | 48 <sup>2</sup><br>+2/-0  | 30 °C /60%<br>RH | 10<br>+0.5/-0   | 13<br>+0.5/-0            | 60 °C/ 60% RH |  |  |

| 6     | Time on Label<br>(TOL) | ≤30 °C /60%<br>RH | TOL                       | 30 °C /60%<br>RH | NA              | NA                       | NA            |  |  |

**Note 1:** CAUTION - To use the "accelerated equivalent" soak conditions, correlation of damage response (including electrical, after soak and reflow), should be established with the "standard" soak conditions. Alternatively, if the known activation energy for moisture diffusion of the package materials is in the range of 0.40 - 0.48 eV or 0.30 - 0.39 eV, the "accelerated equivalent" may be used. Accelerated soak times may vary due to material properties (e.g. mold compound, encapsulant, etc.). JEDEC document JESD22-A120 provides a method for determining the diffusion coefficient.

**Note 2:** The standard soak time includes a default value of 24 hours for semiconductor manufacturer's exposure time (MET) between bake and bag and includes the maximum time allowed out of the bag at the distributor's facility. If the actual MET is less than 24 hours the soak time may be reduced. For soak conditions of 30 °C/60% RH, the soak time is reduced by 1 hour for each hour the MET is less than 24 hours. For soak conditions of 60 °C/60% RH, the soak time is reduced by 1 hour for each 5 hours the MET is less than 24 hours. If the actual MET is greater than 24 hours the soak time must be increased. If soak conditions are 30 °C/60% RH, the soak time is increased 1 hour for each hour that the actual MET exceeds 24 hours. If soak conditions are 60 °C/60% RH, the soak time is increased 1 hour for each 5 hours that the actual MET exceeds 24 hours.

#### **Important Notice and Disclaimer**

LSC reserves the right to make changes to this document and its products and specifications at any time without notice. Customers should obtain and confirm the latest product information and specifications before final design, purchase or use.

LSC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does LSC assume any liability for application assistance or customer product design. LSC does not warrant or accept any liability with products which are purchased or used for any unintended or unauthorized application.

No license is granted by implication or otherwise under any intellectual property rights of LSC.

LSC products are not authorized for use as critical components in life support devices or systems without express written approval of LSC.