# **TW8817 - Digital LCD Panel Processor** with built-in MCU, NTSC/PAL/SECAM Decoder and TCON

Techwell Confidential. Information may change without notice

#### Disclaimer

This d ocument provides t echnical information for the user. Techwell Inc. reserves the right to modif y the information in this document as necessary. The customer should make sure that they have the most recent data sheet version. Techwell Inc. holds no responsibility for any errors that may appear in this document. Customers should take appropriate action to ensure their use of the products does not infringe upon any patents. Techwell Inc. respects valid patent rights of third parties and does not infringe upon or assist others to infringe upon such rights.

TECHWELL, INC.

1 R

# TW8817

# Digital LCD Panel Processor with Video Decoder, MCU and TCON

| Introduction                                                   |      |

|----------------------------------------------------------------|------|

| Applications5                                                  |      |

| Built-in Microcontroller5                                      |      |

| TFT Panel Support5                                             |      |

| On Screen Display5                                             |      |

| Image Control6                                                 |      |

| Power Management6                                              |      |

| Timing Controller (TCON)6                                      |      |

| Miscellaneous6                                                 |      |

| Order Information7                                             |      |

| Functional Description9                                        |      |

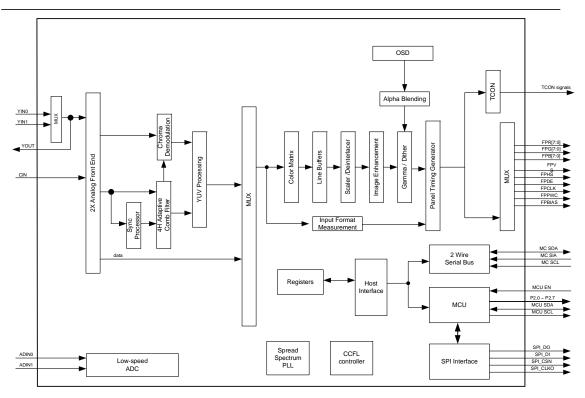

| Overview9                                                      |      |

| Analog Front-end10                                             |      |

| Video Decoder10                                                |      |

| Y/C separation10                                               |      |

| Color demodulation10                                           |      |

| Automatic Chroma Gain Control10                                |      |

| Automatic standard detection11                                 |      |

| Component Processing11                                         |      |

| Digital Input Support                                          |      |

| TFT Panel Support12                                            |      |

| Dithering12                                                    |      |

| Image Control12                                                |      |

| Input Image Control                                            |      |

| Image Scaling                                                  |      |

| Color Space Conversion                                         |      |

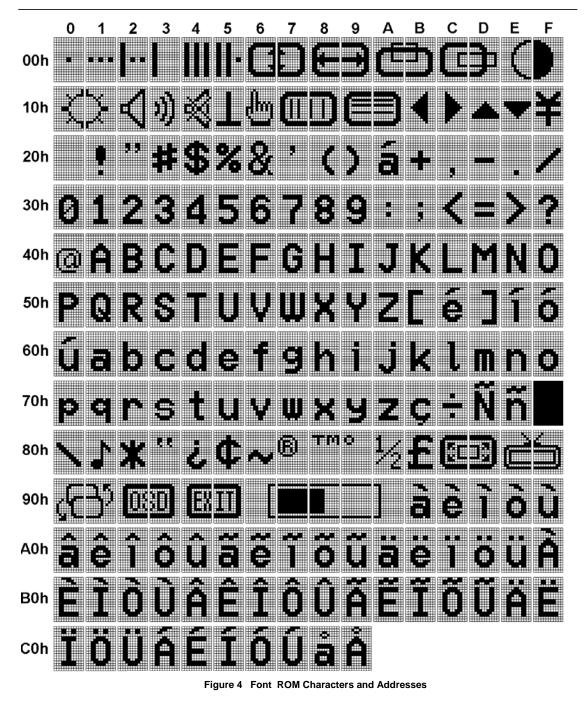

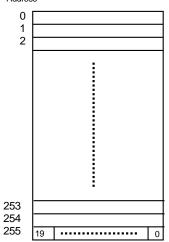

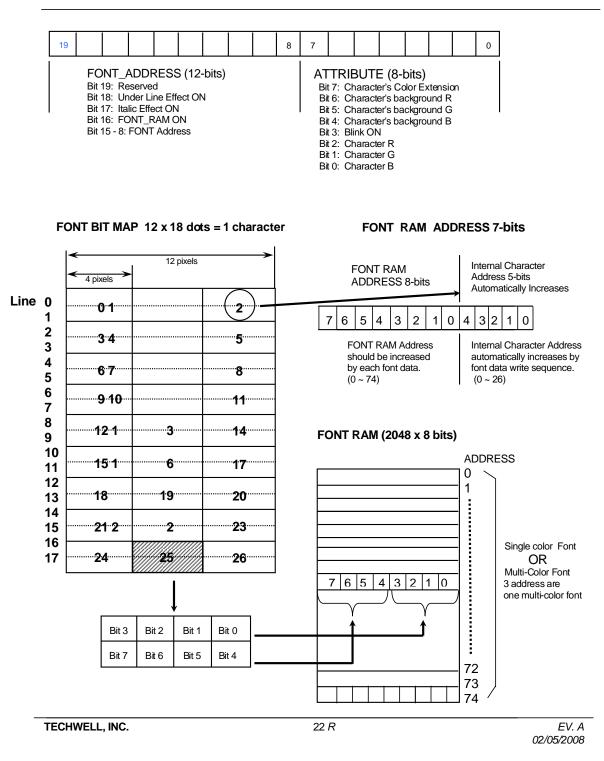

| On Screen Display                                              |      |

| On chip OSD functions                                          |      |

| TW8817 Bassi register setting fbw for Built-in OSD contoller18 |      |

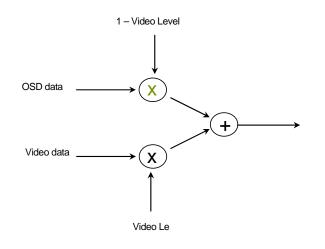

| TW8817 Apha Bending for OSD Window                             |      |

| Microcontroller Interface                                      |      |

| Built-in Minocontroller                                        |      |

| Closed Captioning and Etended Data Services                    |      |

| Test Modes                                                     |      |

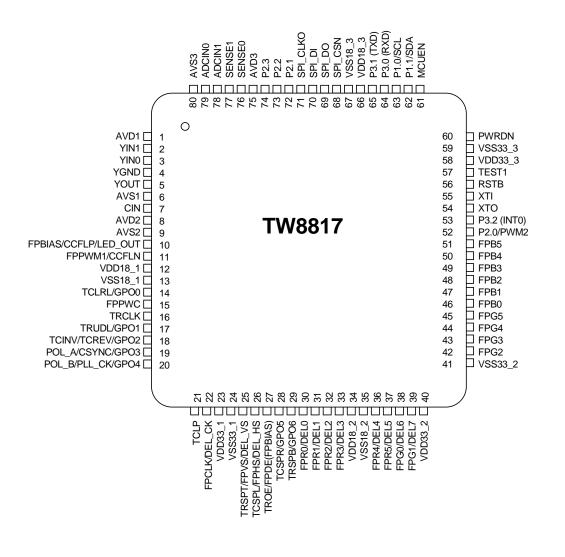

| TW8817 Package Pin Diagram                                     |      |

| Pin Description                                                |      |

| Parametric Information                                         |      |

| AC/DC Electrical Parameters                                    |      |

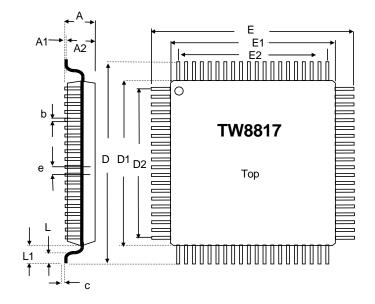

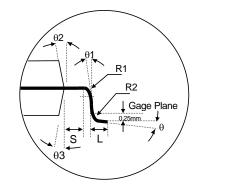

| 80-pin TQFP PackageMechanicalDrawing                           |      |

| TW8817 Register Summary                                        |      |

| General                                                        |      |

| Decoder                                                        |      |

| Decoder(Cont.)                                                 |      |

| LCDC – hputControl                                             |      |

| LCDC - Input Measurement                                       |      |

| LCDC -Scaling                                                  |      |

| LCDC – Image Adjustment                                        |      |

| LCDC –OSD                                                      | FI   |

| LCDC – Display Control                                         |      |

| LCDC -Status & hterrupt43                                      |      |

| LCDC – Power Management                                        |      |

| LCDC – Cobr Enhanement                                         |      |

| LCDC –ETC44                                                    |      |

| LCDC –Gamma                                                    |      |

| DAC44                                                          | Lo   |

| SSPLL                                                          |      |

| CCFLControl45                                                  |      |

| Test Contol and OPO45                                          |      |

| TCON                                                           |      |

| LCDC Sense                                                     |      |

| Test Contol47                                                  |      |

| MCU SIR Register47                                             |      |

| W8817 Registers Description 48                                 |      |

| 0x000-Poduct D Code Reister (ID)                               |      |

| 0x001 – Chip Status Register (CSTATUS)                         |      |

| 0x002 –InputFormat (NFORM)48                                   |      |

| 0x003 – Reserved                                               |      |

| 0x004 – HSYNC Delay Control                                    |      |

| 0x005 – Reserved                                               |      |

|                                                                |      |

|                                                                | 2 PE |

| TECHWELL, INC.                                                 | 2 RE |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | +9                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 0x007 – Cropping Register, High (CROP_H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 49                                                                                                                          |

| 0x008 – Vertical DelayRegister, Low(VDELAY_LO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 49                                                                                                                          |

| 0x009 – Vertical Actve Register, Low (VACTIVE_LO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 50                                                                                                                          |

| 0x00A - Hozontal Deay Register, Low(HDELAY_LO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50                                                                                                                          |

| 0x00B - Hoizontal Active Register, Low(HACTIVE_LO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                             |

| 0x00C -Control Register I(CNTRL1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                             |

| 0x00D –CC Cortrol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 50                                                                                                                          |

| 0x00E –WSS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 51                                                                                                                          |

| 0x00F-WSS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                             |

| 0x010 – BRIGHTNESS Contal Register (BRIGHT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -4                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                             |

| 0x011 – CONTRAST Contol Register (CONTRAST)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 51                                                                                                                          |

| 0x012 – SHARPNESS Contol Register I (SHARPNESS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51                                                                                                                          |

| 0x013 – Chroma (U) Gain Register (SAT_U)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                             |

| 0:014 Oriente (0) Ceir De inter (CAT )()                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -4                                                                                                                          |

| 0x014 – Chroma (V) Gain Register (SAT_V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                             |

| 0x015 –Hue Contol Register (HUE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 52                                                                                                                          |

| 0x017 –Vertical Peaking Contol I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 52                                                                                                                          |

| 0x018 –Coring Control Register (CORING)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                             |

| 0x019 – Delta RGB Mode and ADC Contol Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                             |

| 0x01A – COEDSStatus Register (CC_STATUS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                             |

| 0x01B – CC/EDS Data Register (CC_DATA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 53                                                                                                                          |

| 0x01C Standard Selection (SDT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                             |

| 0x01D – Standard Recognition (SDTR).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                             |

| 0x01E – Component Video Format (CVFMT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 54                                                                                                                          |

| 0x01F-Test Comol Register (TEST)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 54                                                                                                                          |

| 0x020 – Clamping Gain (CLMPG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                             |

| 0x021 –Individual AGC Gan (IAGC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                             |

| 0x022 – AGC Gain (AGCGAIN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 55                                                                                                                          |

| 0x023 – White Peak Threshold (PEAKWT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 55                                                                                                                          |

| 0x024–Clamp level (CLMPL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                             |

| 0x025– Sync Amplitude (SYNCT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 50                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                             |

| 0x026 – Sync Miss Count Register (MISSCNT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                             |

| 0x027 – Clamp Position Register (PCLAMP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55                                                                                                                          |

| 0x028 – Vertical Control I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                             |

| 0x029 –Vertical Control II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                             |

| 0x02A – Cdor Kiler Level Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                             |

| 0x02B – Comb Fiter Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 56                                                                                                                          |

| 0x02C – Luma Delay and HFilter Contol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                             |

| 0x02D – Miscellaneous Contol Register I (MISC1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                             |

| 0x02E – Miscellaneous Contril Register II (MISC2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                             |

| 0x02F-Miscellaneous Contol III (MISC3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 57                                                                                                                          |

| 0x030 – Macrovision Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 58                                                                                                                          |

| 0x031 – Chip STATUS II (CSTATUS2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -0                                                                                                                          |

| 0x032 –H Monitor (HFREF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 58                                                                                                                          |

| 0x033 –CLAMP MODE(CLMD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                             |

| 0x034 – ID Detection Control (NSENSSEN/PSEN//VKTH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 59                                                                                                                          |

| 0x035 –Clamp Contol (CLCNTL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                             |

| 0x038 – Anti-Aliasing Fiter and DecodeContol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                             |

| Flat Panel Display Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                             |

| 0x040to 0x04F – Scaler Input Contol Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 50                                                                                                                          |

| 0x051 b 0x05C- hputFormat MeasurementRegisters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                             |

| 0x060 to 0x06B – Zoom Contol Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                             |

| 0x070to 0x07B – mage Adjustment Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                             |

| 0x07Cto 0x08B – Black/White Stretch Adjustment Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                             |

| 0x092to 0x09D- OSD Contol Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | /1                                                                                                                          |

| 0x092to 0x09D- OSD Contol Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                             |

| 0x092to 0x09D- OSD Contol Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 78                                                                                                                          |